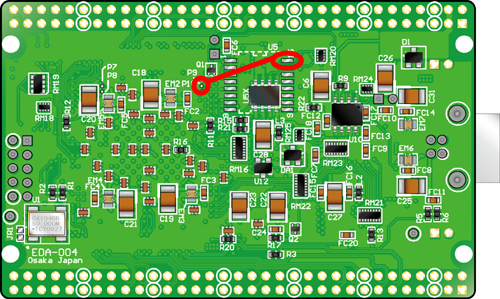

Cyclone III USB-FPGA Board "EDA-004" offers you download-cable-free FPGA develop environment.

HuMANDATA original programming software "BBC [EDA-004]" offers you

- FPGA Configuration

- EPCS Memory Programming (Erase, Write, Verify)

without download cable.

BBC[EDA-004] requires RBF (Raw Binary File) for its operations and Quartus II generates that by easy setting.

Software project file and source codes is opened for customizing. (Borland C++ Builder 2007)

BBC[EDA-004] is tested its operation under these OS below, and is not supported for Mac and Linux.

- Windows XP

- Windows 7 (32bit)

- Windows 7 (32bit) XP mode

- Windows 10

2011/05/13: Initial Release (in Japan)

2011/08/11: Update BBC[EDA-004] - Version 1.1

2012/05/07: Product Revision update, no need to modification.

- Setting of the JP3 (USB Reset from the FPGA)

- FPGA Configuration

- EPCS Memory (Configuration Device) Access

- Option Setting

- Quartus II setting for RBF File generation

- spi_bridge.rbf

- One Hardware Modification (Product Rev.1 only)

- Download

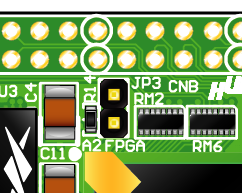

Setting of the JP3 (USB Reset from the FPGA)

Please note that the JP3 must be opened when you use BBC[EDA-004]. A FPGA's pin is connected to FT2232H (USB-to-Serial IC)'s reset pin via JP3.

When it is shorted, Not configured FPGA causes FT2232H reset and your PC would not recognize the EDA-004.

FPGA Configuration

![BBC[EDA-004]FPGA Configuration](https://www.hdl.co.jp/EDA/BBC_EDA004/BBC [EDA-004] Ve882.png)

| Item | Explanation |

|---|---|

| Go | Run an FPGA Configuration. |

| FPGA Reset | The FPGA will be reset. |

FT2232H's B-channel is assigned for FPGA configuration.

Please set the "FPGA configuration mode" to PS (Passive-Serial) mode by setting SW1 (All-ON).

Configuration Device (EPCS Memory) Access

![BBC[EDA-004]EPCS Access](https://www.hdl.co.jp/EDA/BBC_EDA004/BBC [EDA-004] Ve883.png)

| Item | Explanation |

|---|---|

| Go | Start the "Process flow" as set. |

| FPGA Config | Configure the FPGA previously with special RBF file (spi_bridge.rbf) to create a path between FT2232H and EPCS memory. |

| Bulk Erase | Erase all EPCS sectors before downloading. |

| Sector Erase | Erase required numbers of EPCS sectors before downloading. |

| Write | Program a configuration data into EPCS memory. (Uncheck for erase only) |

| Verify | Read-back the programmed data from EPCS and check identity of the data. |

| FPGA Reset | The FPGA will be reset at the end of process. |

FT2232H's A-channel is assigned for configuration device (EPCS memory) access.

Please set the "FPGA configuration mode" to PS (Passive-Serial) mode by setting SW1 (All-ON).

When you configure the FPGA by configuration device's contents set the "FPGA configuration mode" to AS (Active-Serial) mode (SW1 = OFF/OFF/ON/OFF).

(*) Please be care not to configure the FPGA with an inadequately tested design file. It maybe cause damage to the board or peripherals.

Option Setting

![BBC[EDA-004]Option](https://www.hdl.co.jp/EDA/BBC_EDA004/BBC [EDA-004] Ve885.png)

| Item | Explanation |

|---|---|

| Save Current Setting | Each settings of buttons and edit-fields would be saved as ini file when you exit. You can erase ini file contents by uncheck this box and exit the application or delete ini file directly. |

| Use default port description | When EDA-004 does not run with default port desctiption, please uncheck this box. And search specific descriptions using the channel combo-boxes. |

| Channel A (for EPCS Access) | Port description of FT2232H's A-channel used for EPCS memory access (and user communication) |

| Channel B (for FPGA Configuration) | Port description of FT2232H's B-channel used for FPGA configuration. |

| Show System Message | Elaborates message will be printed. (OFF Default) |

| Default | Set the channel combo-boxes to EDA-004's default port description names. |

| Port Detect | You can detect FTDI USB port manually. Please note that not only EDA-004 but also all FTDI's USB port will be detected. |

Quartus II setting for RBF File generation

QuartusII can generate an RBF file of your design by setting as below.

- Open "Device" menu in "Assignments"

- Click "Device and Pin Options..."

- Open "Programming Files" from "Category" and check the "Raw Binary File(.rbf)"

That's all and RBF file will be generated in your project directory.

spi_bridge.rbf

This configuration file will hold the road between FT2232H's A-channel and configuration device (EPCS memory) for downloading configuration data.

Please do not remove it from BBC[EDA-004] directory.

One Hardware Modification (Product Rev.1 only)

Just one hardware modification is needed to operate Configuration Device (EPCS Memory) access.

Please connect the "P9" and the "16th pin of U5" as below.

Click to Zoom

Example picture of modification

Download

| Version | File | |

|---|---|---|

| BBC [EDA-004] Application | 1.1 | |

| Project File (Borland C++ Builder 2007) | 1.1 | Request |

Simple configuration application "BitCfg3" is here. (FPGA configuration only, VC++6.0 project)

BBC[EDA-004] is free software. Please use it at your own risk.

If you have questions or requests, please contact us.

[ ]