CameraLink Signal Capture Demo with Altera Cyclone IV (ACM-024) LVDS I/F

This is simple CameraLink LVDS signal capture demonstration. CameraLink LVDS signals are directly captured by Altera Cyclone IV FPGA board ACM-024, and displayed in TFT LCD. CameraLink signals are generated by an analog CameraLink driver. A cheap CCD camera module is connected to the driver's input.

Components

| Components | ||

|---|---|---|

| Altera Cyclone IV GX FPGA Board | ACM-024 | HuMANDATA |

| Universal board | ZKB-105 | HuMANDATA |

| CameraLink | ACLD-400 (Japanese) | STAC |

| 4.3" LCD Touch Panel Package | TRDB-LTM (Discontinued) |

Terasic UTL-021 is alternative product  5″ Color LCD Display Module with Touch Panel 5″ Color LCD Display Module with Touch Panel |

| Color CCD Camera | TR-1300C (Japanese) | corona-dengyo |

| Download cable | Terasic Blaster | Terasic |

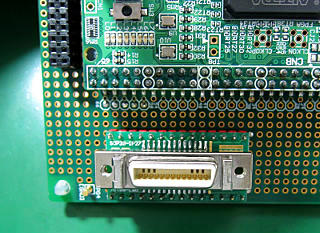

Connector

CameraLink frame grabber connector is "10226-2210PE (3M)". Pins are converted into DIP scale with a conversion board "SOP28-1P27(Aitem-Lab, japanese)".

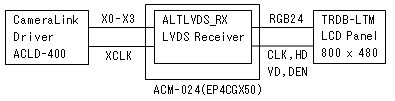

System Architecture

The FPGA receives LVDS signals (data x4, clock x1) from ACLD-400 and transfers RGB data to the LCD.

FPGA Configuration

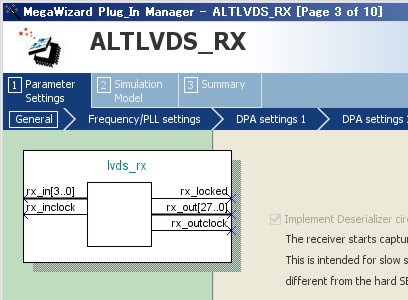

LVDS signals are captured by FPGA internal components generated by MegaWizard "ALTLVDS_RX".

Number of LVDS data signals is 4, so set "Number of Channels" to "4".

CameraLink transfer data in 7bits per one clock in one data-lane. Set "Deserialization Factor" to "7".

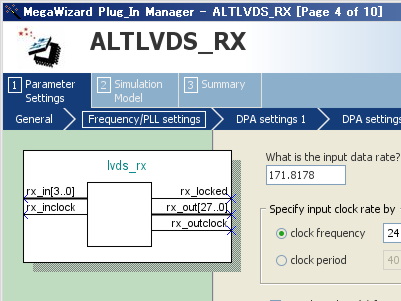

ACLD-400 output clock at 24.5454MHz in NTSC mode, so set "Clock Frequency" to 24.55MHz.

Set "Input Dat Rate" to 171.8178 which multiply "Clock Frequency" by "Deserialization Factor".

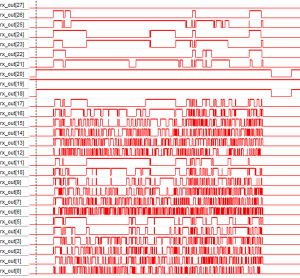

Waveform

| Net Name | Signal | Explanation |

|---|---|---|

| rx_out[27] | Spare | Reserved bit |

| rx_out[20] | DVAL | Frame and Line data is valid |

| rx_out[19] | FVAL | Frame data is valid (Vertical synchronization signal) |

| rx_out[18] | LVAL | Line data is valid (Horizonal synchronization signal) |

| rx_out[22:21],[5:0] | R[7:0] | Red color data |

| rx_out[24:23],[11:6] | G[7:0] | Green color data |

| rx_out[26:25],[17:12] | B[7:0] | Blue color data |

Design Files

We hope you find this demonstration informative.

[]