Could you tell me how to use DDR2SDRAM?

We have access tests when their manufacturing test. Here is a part of steps to implement a memory access component with ALTMEMPHY and a NiosII processor.

This example is bases on ACM-025 (Arria II) but is also useful for Cyclone IV FPGA boards below.

Environment

Quartus II Version 11.0 SP2

DDR2 SDRAM Controller with ALTMEMPHY v11.0 (Build 208)

Add a memory controller component

First, start SOPC Builder and add a processor core, internal memory, and others.

Then add a component, "DDR2 SDRAM Controller with ALTMEMPHY", from "Component Library"DDR2SDRAM to access a DDR2SDRAM.

Settings of ALTMEMPHY

In "Memory Settings" tab, we configure memory parameters.

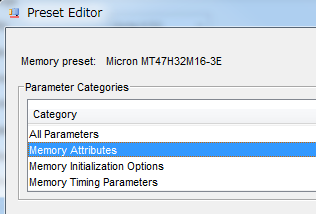

Set filters as below and select a "MT47H32M16-3E" because a DDR2 memory "MT47H64M16HR-3" set on ACM-025 board is not listed.

- Memory vendor = Micron

- Memory format = Discrete Device

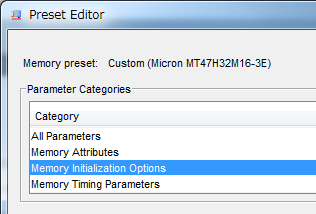

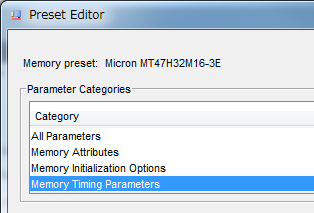

Select a "MT47H32M16-3E", and click "Modify parameters...". For specific parameters, please refer to a datasheet of DDR2 memory "MT47H64M16HR-3".

Here is tables of parameters include default values and modified ones for reference. The others are not modified.

2Gb density DDR2 memory is available as custom order. (part no. is "MT47H128M16RT-25E")

Please change "Row address width" to "14". Please check other timing parameters by yourself.

Reference datasheets and Web pages

- Altera, External memory interface handbook

- Micron, DDR2SDRAM, MT47H128M16RT-25E webpage

- Micron, DDR2SDRAM, MT47H64M16HR-3 webpage

Design Files

We do not offer sample design files. If you have any questions, please feel free to contact us.

[kw] 2013-01-15 ACM-025 ACM-024 ACM-108 DDR2SDRAM ALTMEMPHY QuartusII Nios

[ ]